# © EPoS

## TF: Advanced Packaging

- The European Chips Act supported by accompanying focused R&D&I projects on "Advanced packaging technologies for highest performance and integration density" in the KDT JU / Chips JU could mark a turning point and open up the chance to bring advanced packaging and manufacturing back to Europe.

- Advanced packaging\* generally groups a variety of different techniques and technologies to realize electronic components including 2.5D, 3D-IC, wafer level packaging, SiPs, SoC, power modules

- Heterogenous integration\* refers to the integration of separately manufactured components into a higher-level assembly (System-in-Package, SiP) that, in the aggregate, provides enhanced functionality and improved operating characteristics

## Why should Europe invest in Advanced Packaging?

Innovation and Competitiveness: Investing in advanced packaging can help European companies stay ahead in the global market.

• **Environmental Sustainability:** By investing in sustainable packaging solutions, Europe can meet the growing demand for eco-friendly products.

Economic Growth: The advanced packaging presents significant economic potential such as job creation, revenue generation, & export opportunities.

**Technological Leadership:** By investing in advanced packaging, Europe can establish itself as a leader in cutting-edge products.

Societal Challenges: Through advanced packaging solutions, Europe can contribute to improving the quality of life and addressing societal needs.

Advanced Packaging can position Europe as a hub for sustainable, innovative, and competitive products, driving economic growth, and technological advancement.

## Advanced Packaging – global perspective

- Exploring the Impact of Industry-Government Co-Investments for the Advanced Electronic Sector in North America, Asia and Europe

- Representative from: Europe, India, Korea, USA, Canada

- CHIPS Roundtable Chat: Pilot Line Fireside Chat

- Representative from India, Germany, Japan, USA

- On every continent there are investments in packaging and advanced packaging

### Exploring the Impact of Industry-Government Co-Investment: for the Advanced Electronics Sector in North America, Asia and Europe

In an era defined by technological advancement and digital transformation, the semiconductor and microelectronics packaging industry plays an important role in shaping the global economy and innovation landscape. The introduction of the CHIPS and Science Act (Creating Helpful Incentives to Produce Semiconductors for America) in the United States. Since then other key countries and regions have outlined similar programs to invest in the microelectronics industry growth. In Europe, the European Chips Act has generated significant interest and discussion. This special session aims to dive deeper into the multifaceted opportunities offered by the CHIPS Acts, as well as their potential impact on the semionductor and microelectronics packaging industry in North America, Europe and Asia. The speakers will address the potential economic benefits of the government led programs and co-investments for the United States, Europe, India and Japan, including job creation, supply chain resilience, and enhanced technological

innovation. We will examine the prospects of global collaborations and partnerships between national semiconductor and microelectronic packaging centers and industry leaders. The panel will also discuss

mechanisms for knowledge exchange, joint research initiatives, and mutually beneficial outcomes,

Dr. Kwang-Seong Cho

Link ECTC

2024 IEEE 74th Electronic Components and Technology Conference | Denver, Colorado | May 28 – May 31, 202-

### HIR Special Sessions at ECTC 2024

Session 1: Challenges and innovations in Thermal Engineering from Pan-out to 2.50 and 30 stacking

Thermal challenges for stacked die systems

Session 2: Engineering Chipiets for the Al Era

iplet Trends, Choices, and Directions for the Al Data Center

Future of Al Hardware Enabled by Advanced Packaging

Engineering Chiplets for AI

### Session 3: CHIPS Roundtable Chat: Pilot Line Fireside Chat

Design, Semiconductor, Packaging and Systems R&D in India

European Chips Act and the Arist – Pivib Pilot Lini

Rapidus Fackaging Filot Line

ECTC Roundtable Pilot Line Discussion AlM Photonics

HIR Session 4: Packaging Challenges and Innovation for Future Communication Systems

Frontend Packaging and Integration Trends for mmWave and Sub-THz Phased Array

Link IEEE EPS HIR at ECTC

## CSA Pack4EU

- Creation of a Pan-European network for Advanced packaging and a Roadmap to boost packaging in and for Europe

- 07.2023 06.2024

- June, 12 the project presented its final recommendations to the European commission.

- Ended with 9 recommendations to boost Advanced Packaging in Europe

- High-Level Committee on AP

- AP Expert Group to feed the L2F

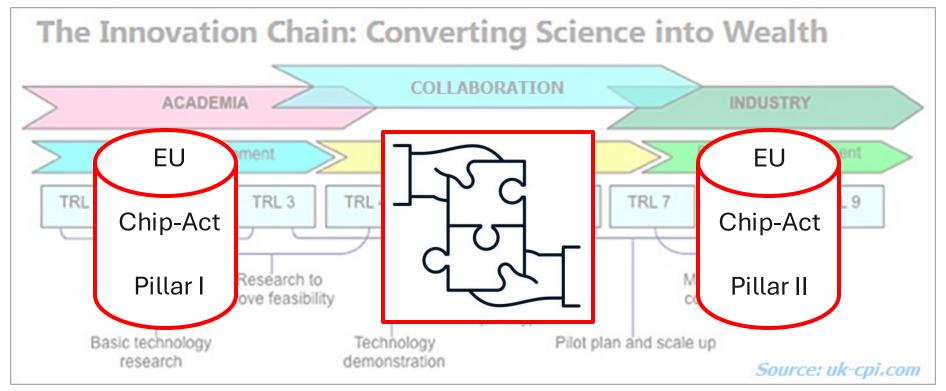

## EU Chips Act: the missing Pillar

Focusing on new technologies

"FAB-in-the-LAB" | "LAB-in-the-FAB"

Focusing on new product needs

## Create the seeds for future volume production & economic security

**2TOS**

### Chips JU RTO Pilot Lines

### Objective:

Prototyping up to small volume manufacturing for specific solutions

INDUSTRY LEAD CONSORTIA (LES, SMES, Lab to Fab Accelerator – PL 3: Advanced Packaging

Lab to Fab Accelerator – PL1: 2nm FinFet

Lab to Fab Accelerator - PL2: 7nm FD SOI

Lab to Fab Accelerator – PL: Power Electronics

Acc. Synergies

## Objective:

Projects accelerating the Lab to Fab technology transfer from RTO PLs to industry

## EPoSS TF activities towards the first Lab-to-Fab Accelerator program

PL calls and decision

Set-up of expert group for APECS line

Workshops on accelerator projects for APECS pilot line → input for WP 2025

WP 2025 + calls 2025

Start of first accelerator project

Q1/2024 Q2/2024 Q3/2024 Q4/2024 ab Q1/2025

14.02.2024: **WS on PL 3 @Fraunhofer IZM**

16.04.2024: **Session on Lab-to-fab accelerators at SSI 2024, Hamburg**

June 12: Subjects presented to Chips JU GB July, 1:

■PAB asked Chips JU ED to prepare first L2F call in WP 2025 Sept, 12 @ESTC: WS on L2F with participants

Oct / November: WP 2025 draft and approval by PAB/ GB

May, 2024: Expert group installed; bullet point lists for initial discussion collected

June 27 2024: Open **Workshop of experts** (on-line)